Logic Diagram For 3 8 Decoder 29+ Images Result

Logic Diagram For 3 8 Decoder. The resulting logic circuit for the 3:8 decoder is as follows. Asked jul 9, 2020 in computer by abha01 (51.6k points)

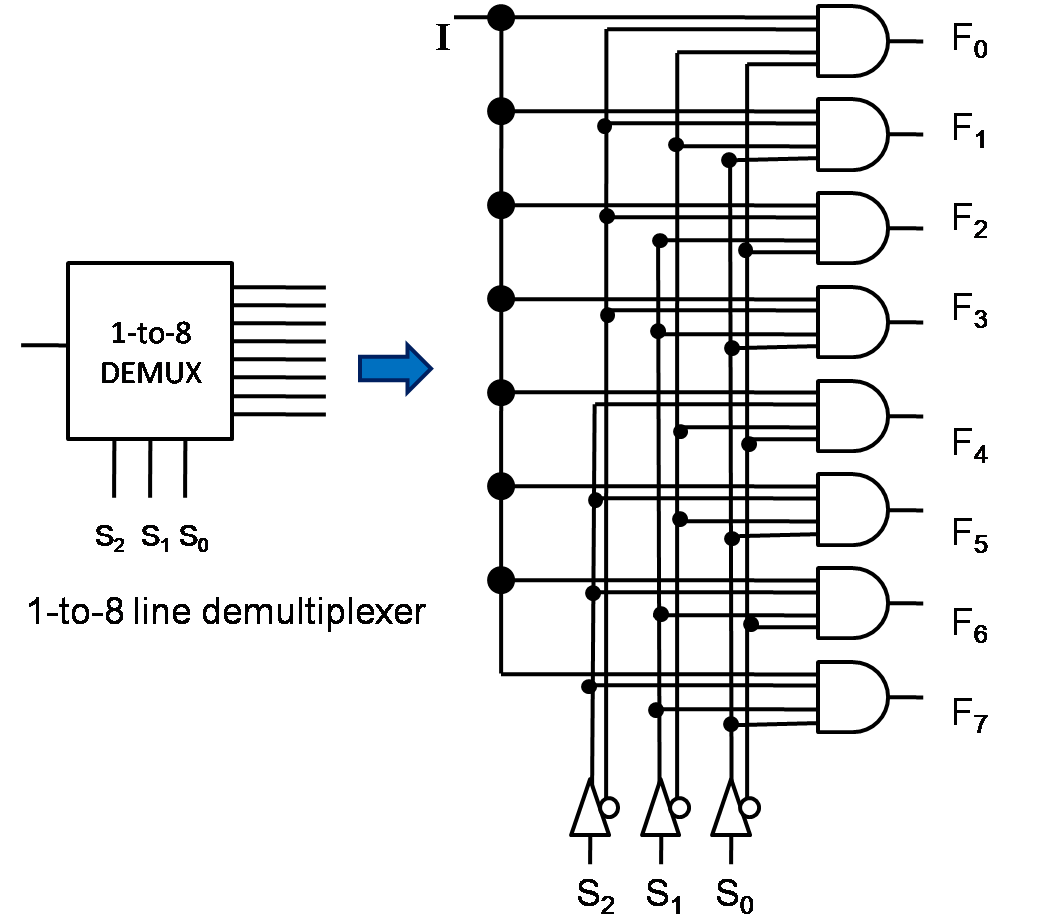

For simple encoders, it is assumed that only one input. Functional diagram 001aag752 3 to 8 decoder enable exiting a0 1 a1 2 a2 3 e1 4 e2 5 e3 6 15 y0 14 y1 13 y2 12 y3 11 y4 10 y5 9 y6 7 y7 fig. The flatpak version has the.

91 e4od transmission wiring diagram home fax wiring diagram dodge wiring harnes diagram 1997 window switch wire diagram 4

Decoder Logic Diagram And Truth Table Wiring Diagram Schemas

Input is taken as 3, and the outputs are 8 (i.e. Thus, for example, if {c b a} = 100, then y4 is selected; Here in the given figure, one case is highlighted when d7 input is ‘1’ all outputs a = 1, b=1, and c=1. You can verify other combinations from.

Source: robhosking.com

Required number of lower order decoders=m 2 /m 1. It has 3 input lines and 8 output lines. Here in the given figure, one case is highlighted when d7 input is ‘1’ all outputs a = 1, b=1, and c=1. Based on the 3 inputs one of the eight outputs is selected. Thus, for example, if {c b a} =.

Source: electroniclinic.com

From the truth table, it is seen that only one of eight outputs (do. But note that among 4 decoders present on the right side only one decoder is active at a time and one decoder response to the result. Now we know possible outputs for 3 inputs, so construct 3 to 8 decoder, having 3 input lines, a enable.

Source: multisim.com

Decoder block diagram 3 to 8 decoder. Thus, for example, if {c b a} = 100, then y4 is selected; Altogether 5 3 to 8 decoders are required to produce 32 output lines of 5 to 32 decoders. But note that among 4 decoders present on the right side only one decoder is active at a time and one decoder.

Source: youtube.com

Required number of lower order decoders=m 2 /m 1. The inputs are c, b, and a (c is the msb and a is the lsb). The input becomes output and vice versa. The block diagram of 4 to 16 decoder using 3 to 8 decoders is shown in the following figure. The truth table for 3 to 8 decoder is.

Source: wiring08.blogspot.com

The block diagram of 4 to 16 decoder using 3 to 8 decoders is shown in the following figure. Now we know possible outputs for 2 inputs, so construct 2 to 4 decoder , having 2 input lines, a enable input and 4 output lines. It has 3 input lines and 8 output lines. The complement of input a3 is.

Source: wiringschemas.blogspot.com

The inputs are c, b, and a (c is the msb and a is the lsb). We can use the following formulae to calculate the number of lower order decoders (2:4) required to form a higher order decoder like 3:8 decoder. This decoder circuit gives 8 logic outputs for 3 inputs. Decoder block diagram 3 to 8 decoder. 3 to.

Source: chegg.com

In 3 * 8 decoder we have 3 input lines and 8 output lines and will just select one output line based on various input combinations. Required number of 3 to 8 decoders= =2. The following figure shows the block diagram of a decoder. The circuit is designed with and and nand logic gates. The resulting logic circuit for the.

Source: electroniclinic.com

10 rows 3 to 8 line decoder circuit is also called a binary to an octal decoder. Write the truth table and draw the logic circuit diagram for a 3 to 8 decoder and explain its working. Here in the given figure, one case is highlighted when d7 input is ‘1’ all outputs a = 1, b=1, and c=1. In.

Source: instrumentationtools.com

Altogether 5 3 to 8 decoders are required to produce 32 output lines of 5 to 32 decoders. For simple encoders, it is assumed that only one input. An encoder is a combinational circuit that converts binary information in the form of a 2 n input lines into n output lines, which represent n bit code for the input. It.

Source: autosportswiring.com

Draw the circuit diagram for a 3 to 8 decoder. Required number of lower order decoders=m 2 /m 1. From the truth table, it is seen that only one of eight outputs (do. The complement of input a3 is connected to enable e of lower 3 to 8 decoder in order to get the outputs y 7 to y 0..

Source: slideserve.com

The logical diagram of the 3×8 line decoder is given below. Decoder block diagram 3 to 8 decoder. Required number of lower order decoders=m 2 /m 1. The truth table is as follows: Asked jul 6, 2020 in computer by rupabharti (50.8k points) icse;

Source: tinyu.me

Here in the given figure, one case is highlighted when d7 input is ‘1’ all outputs a = 1, b=1, and c=1. Altogether 5 3 to 8 decoders are required to produce 32 output lines of 5 to 32 decoders. The parallel inputs a 2, a 1 & a 0 are applied to each 3 to 8 decoder. The input.

Source: in.pinterest.com

Therefore, we require two 3 to 8 decoders for implementing one 4 to 16 decoder. Logic symbol 001aag753 3 to 8 decoder enable exiting a0 1 a1 2 a2 3 e1 4 e2 5 e3 6 y0 15 y1 14 y2 13 y3 12 y4 11 y5 10 y6 9 y7 7 fig. The circuit is designed with and and.

Source: electronics.stackexchange.com

But note that among 4 decoders present on the right side only one decoder is active at a time and one decoder response to the result. Based on the 3 inputs one of the eight outputs is selected. The block diagram of 4 to 16 decoder using 3 to 8 decoders is shown in the following figure. The input becomes.

Source: vlsi-design-engineers.blogspot.com

Here in the given figure, one case is highlighted when d7 input is ‘1’ all outputs a = 1, b=1, and c=1. Required number of lower order decoders=m 2 /m 1. If {c b a} = 011, then y3 is selected; 15 3 to 8 decoder logic diagram. The complement of input, a3 is connected to enable, e of lower.

Source: electroniclinic.com

The 3 to 16 line decoder can be constructed using either 2 to 4 decoder or 3 to 8 decoder. The truth table is as follows: Input is taken as 3, and the outputs are 8 (i.e. The following figure shows the block diagram of a decoder. Logic symbol 001aag753 3 to 8 decoder enable exiting a0 1 a1 2.

Source: electroniclinic.com

For the different functions in the truth table, the minterms can be written as 1,2,4,7, and similarly, for the borrow, the minterms can be written as 1,2,3,7. Now we know possible outputs for 3 inputs, so construct 3 to 8 decoder, having 3 input lines, a enable input and 8 output lines. 3 to 8 decoder with truth table and.

![[GZ_1103] Logic How To Build A 4 To 16 Decoder Using Only [GZ_1103] Logic How To Build A 4 To 16 Decoder Using Only](https://i2.wp.com/static-cdn.imageservice.cloud/8080905/ekt-121-4-digital-electronics-1-ppt-download.jpg)

Source: cular.phae.mohammedshrine.org

The flatpak version has the. Functional diagram 001aag752 3 to 8 decoder enable exiting a0 1 a1 2 a2 3 e1 4 e2 5 e3 6 15 y0 14 y1 13 y2 12 y3 11 y4 10 y5 9 y6 7 y7 fig. Now we know possible outputs for 2 inputs, so construct 2 to 4 decoder , having 2.

Source: wiringideas.blogspot.com

From the truth table, it is seen that only one of eight outputs (do. We can use the following formulae to calculate the number of lower order decoders (2:4) required to form a higher order decoder like 3:8 decoder. It is convenient to use an and gate as the basic decoding element for the output because it produces a “high”.

Source: radiosets.tpub.com

Thus, for example, if {c b a} = 100, then y4 is selected; It is convenient to use an and gate as the basic decoding element for the output because it produces a “high” or logic “1” output only when all of its inputs are logic “1”. An encoder is a combinational circuit that converts binary information in the form.