Block Diagram Vhdl 42++ Images Result

Block Diagram Vhdl. I placed vhdl blocks including generics which are seen as parameters in the bdf. International journal of science, engineering and technology research (ijsetr) volume 8, issue 1, january 2019, issn:

The design will first be completed and simulated. Designing 8 bit microprocessor using vhdl. If you want to change the diagram because you have more/less element before or after the item node, you have only to add/remove elements from the left/right matrices, change the factor who divide \myheight and adjust.

1999 saturn sc1 engine diagram ignition starter switch wiring diagram xbox wireles controller diagram 2002 mercury sable fuse box diagram

VHDL设计简单数字时钟_中二病也要写博客CSDN博客

Many of the xilinx example designs for ip cores come in text vhdl/verilog format even though they are mostly based on standard ip blocks. If your hdl design is in large part structural, it may be easier for you to enter its description graphically as a block diagram, rather than writing the source code. This answer is not useful. Is there a way in vivado to create a block design or a diagram from a vhdl and/or verilog deign, which is mostly based on standard ip cores?

Source: kd2boa.blogspot.com

How to convert a vhdl (.vhd) file to a symbol file (.bsf), and then insert that symbol in a block diagram/schematic file (.bdf). If you want to change the diagram because you have more/less element before or after the item node, you have only to add/remove elements from the left/right matrices, change the factor who divide \myheight and adjust. Its.

Source: ikr.uni-stuttgart.de

If you want to convert your block design file (.bdf ) file to your vhdl code. The processes can be implemented using state diagrams, truth tables or hdl text. Samuel cancel, malik roberts, demi lopez and freddy pender The block diagram editor allows you to graphically represent vhdl processes or verilog always statements. The design will first be completed and.

Source: kd2boa.blogspot.com

This project is to design an 8 bit microprocessor using vhdl. A gray rectangle is the simcon 3.1 board and white one is a fpga chip. $$z_8$$ is the extra bit which will be used to store the bit of the $$s^{(.)}$$ term to the left of the divisor’s msb. A lot of times i'm handed a vhdl project, consisting.

Source: researchgate.net

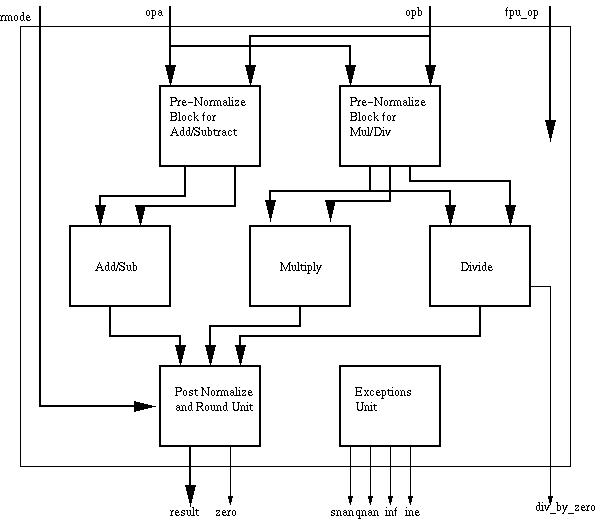

Many of the xilinx example designs for ip cores come in text vhdl/verilog format even though they are mostly based on standard ip blocks. The design will first be completed and simulated. There i can set a parameter e.g:. The processes can be implemented using state diagrams, truth tables or hdl text. Figure 4 shows a block diagram of vhdl.

Source: chegg.com

Show activity on this post. If you want to change the diagram because you have more/less element before or after the item node, you have only to add/remove elements from the left/right matrices, change the factor who divide \myheight and adjust. The processes can be implemented using state diagrams, truth tables or hdl text. Many of the xilinx example designs.

Source: allaboutcircuits.com

In cases like that it is very desirable to have a block diagram view. A lot of times i'm handed a vhdl project, consisting a hierarchy of components, and no accompanying documentation. There i can set a parameter e.g:. The block diagram editor allows you to graphically represent vhdl processes or verilog always statements. Once the simulation proves successful the.

Source: pinterest.com

There i can set a parameter e.g:. I then have to go through the painstaking process of combing through the code, cataloging the components, figuring out the hierarchy and trying to draw my own block diagram. A gray rectangle is the simcon 3.1 board and white one is a fpga chip. Designing 8 bit microprocessor using vhdl. Figure 4 shows.

Source: slideserve.com

Hello, please tell me if i got something wrong in my workflow: The design will first be completed and simulated. Once the simulation proves successful the vhdl will be put onto a fpga. A lot of times i'm handed a vhdl project, consisting a hierarchy of components, and no accompanying documentation. Vhdl design of digital stop watch.

Source: youtube.com

If you want to change the diagram because you have more/less element before or after the item node, you have only to add/remove elements from the left/right matrices, change the factor who divide \myheight and adjust. This approach visualizes the data flow inside a single diagram. Once the simulation proves successful the vhdl will be put onto a fpga. Samuel.

Source: fpgalanguages.com

The design will first be completed and simulated. There i can set a parameter e.g:. How to convert a vhdl (.vhd) file to a symbol file (.bsf), and then insert that symbol in a block diagram/schematic file (.bdf). This project is to design an 8 bit microprocessor using vhdl. If your hdl design is in large part structural, it may.

Source: blog.csdn.net

The editor supports the use of generics/parameters (both in the interface definition and in the diagrams), complex port maps, (vhdl) records, etc. Is there a way in vivado to create a block design or a diagram from a vhdl and/or verilog deign, which is mostly based on standard ip cores? Its not open source software, but it is free to.

Source: kd2boa.blogspot.com

$$z_8$$ is the extra bit which will be used to store the bit of the $$s^{(.)}$$ term to the left of the divisor’s msb. The block diagram editor will then convert the diagram automatically into structural vhdl, verilog or edif netlist. The altera up2 development board includes the flex10k fpga that will be used. This project is to design an.

Source: chegg.com

The processes can be implemented using state diagrams, truth tables or hdl text. Samuel cancel, malik roberts, demi lopez and freddy pender This approach visualizes the data flow inside a single diagram. A gray rectangle is the simcon 3.1 board and white one is a fpga chip. Facilitating an abstraction level between block diagrams and plain hdl code, the block.

Source: researchgate.net

Show activity on this post. This answer is not useful. I placed vhdl blocks including generics which are seen as parameters in the bdf. This approach visualizes the data flow inside a single diagram. This project is to design an 8 bit microprocessor using vhdl.

Source: researchgate.net

A lot of times i'm handed a vhdl project, consisting a hierarchy of components, and no accompanying documentation. If you want to change the diagram because you have more/less element before or after the item node, you have only to add/remove elements from the left/right matrices, change the factor who divide \myheight and adjust. This answer is not useful. In.

Source: sites.google.com

Once the simulation proves successful the vhdl will be put onto a fpga. Facilitating an abstraction level between block diagrams and plain hdl code, the block diagram editor allows you to graphically represent cooperating vhdl processes or verilog always statements. I then have to go through the painstaking process of combing through the code, cataloging the components, figuring out the.

Source: web.cecs.pdx.edu

Is there a way in vivado to create a block design or a diagram from a vhdl and/or verilog deign, which is mostly based on standard ip cores? There i can set a parameter e.g:. The block diagram editor allows you to graphically represent vhdl processes or verilog always statements. The block diagram editor will then convert the diagram automatically.

Source: verificationacademy.com

Select the clear, load and dat_in nets (or the ports with these names on instances i0 and i1).choose autoconnect from the autoroute cascade of the popup menu. Is there a way in vivado to create a block design or a diagram from a vhdl and/or verilog deign, which is mostly based on standard ip cores? Figure 4 shows a block.

Source: acmesystems.it

The block diagram editor is a tool for graphical entry of vhdl, verilog and edif designs. Once the simulation proves successful the vhdl will be put onto a fpga. The large rectangle around the diagram is crossed by 3 arrows, representing the input and output ports of the vhdl entity. Facilitating an abstraction level between block diagrams and plain hdl.

Source: pinterest.com

The editor supports the use of generics/parameters (both in the interface definition and in the diagrams), complex port maps, (vhdl) records, etc. The block diagram editor allows you to graphically represent vhdl processes or verilog always statements. Select the clear, load and dat_in nets (or the ports with these names on instances i0 and i1).choose autoconnect from the autoroute cascade.